ISSN: 2252-8814, DOI: 10.11591/ijaas.v13.i2.pp325-332

# CHBMLI based DSTATCOM for power quality improvemt in a three-phase three-wire distribution system with PI controller

Thiruveedula Madhu Babu<sup>1</sup>, Kalagotla Chenchireddy<sup>2</sup>, Kama Sreevarsha<sup>1</sup>, Badudhala Praveen<sup>1</sup>, Mohammad Thanveer<sup>1</sup>, Ganji Kashinadh<sup>1</sup>

<sup>1</sup>Department of Electrical and Electronics Engineering, Teegala Krishna Reddy Engineering College, Hyderabad, India <sup>2</sup>Department of Electrical and Electronics Engineering, Geetanjali College of Engineering and Technology, Hyderabad, India

#### **Article Info**

## Article history:

Received Sep 30, 2023 Revised Jan 11, 2024 Accepted Mar 6, 2024

## Keywords:

CHBMLI DSTATCOM Harmonics Power quality Reactive power

#### **ABSTRACT**

This paper presents a cascaded h-bridge (CHB) multilevel inverter (MLI) based MLI based distribution static synchronous compensator (DSTATCOM). The main objective of this paper is to reduce source current harmonics in the distribution system by using a cascade H-bridge multilevel inverter (CHBMLI) as DSTATCOM with a proportional-integral (PI) controller. The PI controller compensates reactive power, reduces source current harmonics, and maintains the unity power factor in the distribution system. The conventional two-level inverter-based DSTATCOM has many disadvantages such as high total harmonic distortion (THD), and high switching stress power semi-conductor devices, suitable for only low-power applications. This paper to overcome these drawbacks by using MLI-based DSTATCOM. The proposed system simulations are verified in MATLAB/Simulink software. The verified results are source current, load current, and compensating current.

This is an open access article under the CC BY-SA license.

325

## Corresponding Author:

Thiruveedula Madhu Babu

Department of Electrical and Electronics Engineering, Teegala Krishna Reddy Engineering College Medbowli, Meerpet, Saroornagar, Hyderabad–500097, Telangana, India

Email: madhumk448@gmail.com

# 1. INTRODUCTION

In particular, a five-level voltage inverter with an H-bridge topology is the subject of the study's analysis of energy indicators for multilevel voltage converters. The rising demand for energy-efficient technological processes, power-efficient semi-conductor converters, and accurate reactive power level regulation fuels the importance of the study. Two-stage, three-phase circuits coupled in a wye configuration are used by the inverter in question [1]. In this work, a brand-new converter design for tying three-phase photovoltaic (PV) panels to the grid is presented. The converter uses a distinctive topology in the five-level class and only a few power semiconductor switches. The solar source, a two-phase inverter, and a Scott-t transformer that transforms the inverter's two-phase output into three phases for grid connection make up the converter's three primary components [2]. In this research, a novel method for a three-phase, five-level multilevel inverter (MLI) with a five-level output voltage is presented. Traditionally, a three-phase full-bridge circuit and an extra bidirectionalswitch have been employed to achieve the 5-level output voltage by splitting a direct current (DC) voltage source using two capacitors. However, this strategy has produced issues including capacitor voltage imbalances and output voltage restrictions [3]. The switching angles of threephase five-level cascade H-bridge MLI with unknown switching angles are introduced in this research using a novel way. The selective harmonic elimination pulse width modulation (PWM) approach is used across a wide range of modulation indices to improve total harmonic distortion (THD). The idea entails connecting two

Journal homepage: http://ijaas.iaescore.com

326 ISSN: 2252-8814

of these inverter modules in series with switched-capacitor units (SCUs) that are 2L in size [4]. By adjusting the output current of the DC bus, this technique aims to provide an inverter output that has five levels.

The method is based on the modulation scheme of a current source inverter with five levels. This approach modifies the switching state of the inverter as well as the DC bus current using logical transformations. As a result, it makes it possible for the current source inverter to provide a five-level output without needing more [5], [6]. The problem of harmonics in solar PV energy conversion systems, which can impair power quality, is discussed in this work. Proportional integral (PI), artificial neural network (ANN), and fuzzy logic (FL) controllers are three alternative controller systems that are used to reduce harmonics in a solar-powered cascaded fifteen-level inverter [7]. The unified power quality conditioner (UPQC), an MLIbased cascaded H-bridge (CHB) solution, is presented in the study as a novel approach to resolving various power quality problems. These issues include reactive power compensation, current unbalance, reactive power harmonics, voltage harmonics, and voltage sag. Six H-bridges and three DC link capacitors are used in the proposed method's three-level UPQC [8]-[10]. The UPQC is described in the study as a vital tool for improving power quality in a power system. The research focuses on a reduced switch MLI that is managed by a soft computing ANN. Several power quality issues, such as voltage sag, voltage swell, power factor, harmonics, and voltage compensation restoration time are intended to be mitigated by this new configuration [11], [12]. The UPQC, a significant power conditioner designed to enhance power quality for consumers and utility points, is discussed in the paper's discussion of the importance of power systems. A five-level output produced by the UPQC's series and shunt controllers is filtered to provide compensatory signals. The voltage and current profiles in the power distribution system are improved by these signals [13]-[15]. To comply with utility grid power quality standards for harmonic currents and voltages, the article discusses the requirement for active power filters in contemporary power systems. For both balanced and unbalanced nonlinear loads, the emphasis is on lowering THD in source currents and correcting for reactive power. The article introduces a shunt active power filter (SAPF), a 3-phase 5-level CHB-based multi-level inverter (MLI), to do this [1], [16]–[19].

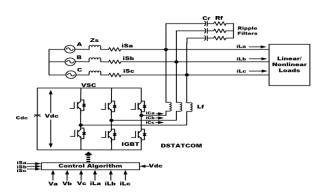

## 2. DSTATCOM

Figure 1 shows the distribution static synchronous compensator (DSTATCOM) topology. A DSTATCOM stands for distribution static compensator. It is a type of power electronic device used in the field of electrical power distribution and quality control [20]–[24]. A DSTATCOM is designed to improve the quality of electrical power in distribution systems by mitigating power quality issues such as voltage sag, voltage swell, flicker, and harmonics. It can also provide reactive power compensation.

Figure 1. DSTATCOM topology

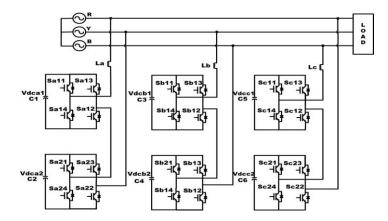

# 2.1. Proposed DSTATCOM topology

Figure 2 shows the proposed DSTATCOM topology. A 5-level inverter using a CHB and PI Controller to improve power quality in the distribution system is shown in the Figure 2. A 3-phase 5-level inverter in the system directs a 3-phase supply with R, Y, and B phases to a non-linear load. There are two capacitors and eight switches in this inverter. An inductor connects the inverter to the power supply's two separate phases. insulated-gate bipolar transistors (IGBT) are used in the switches, and they each have a parallel-connected diode. To provide a voltage rating greater than the IGBT reverse-blocking voltages, the IGBT modules are connected in series. The voltage of the capacitor Vdca1 must be half or less of the required voltage level. Filter reactors, often referred to as La, Lb, and Lc inductors, are used to remove undesirable

harmonics from the three-phase electric power system or transmission line. The single phase (R) through a filter reactor (La) serves as the source of power for the multi-level inverter. To control larger voltage ratings, the IGBTs are connected in series. The IGBT's switching pattern determines how and when the capacitor charges and discharges. When switches Sa11, Sa12, Sa24, and Sa23 are ON, capacitors discharge continually, and the alternation of charging and discharging balances the voltage of the capacitors. To do this, sensor-less voltage balancing is combined with sinusoidal pulse width modulation with level shifting. Voltages from capacitors are gathered, sent to the Y-phase, and repeated for the other connections. When gathered, the capacitor voltages are applied to a non-linear load to reduce THD.

Figure 2. Proposed DSTATCOM topology

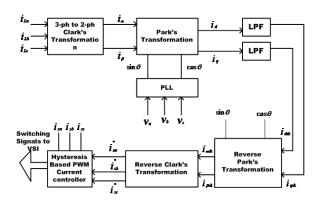

## 3. SYNCHRONOUS REFERENCE FRAME THEORY

Figure 3 shows the synchronous reference frame theory. The voltage at the point of common coupling [PCC] or PCC (Vs) is transformed to the rotating reference frameas a result of the ABC-do conversion utilizing Park's transformation. Low-pass filters (LPFs) remove oscillatory and harmonic components from voltages. The following is how PCC determines the load voltage's [VL] amplitude:

$$V_{a} = V_{m} Sin (wt)$$

$$V_{a} = V_{m} Sin \left(wt - \frac{2\pi}{3}\right)$$

$$V_{c} = V_{m} Sin \left(wt - \frac{4\pi}{3}\right)$$

(1)

$$i_{La} = \sum I_{Lan} Sin\{n(wt) - \theta_{an}\}$$

$$i_{Lb} = \sum I_{Lbn} sin\left\{n\left(wt - \frac{2\pi}{3}\right) - \theta_{bn}\right\}$$

$$i_{lc} = \sum I_{Lcn} Sin\left\{n\left(wt - \frac{2\pi}{3}\right) - \theta_{cn}\right\}$$

(2)

$$i_{lc} = \sum I_{Lcn} Sin \left\{ n \left( wt - \frac{2\pi}{3} \right) - \theta_{cn} \right\}$$

$$\begin{bmatrix} i_{\alpha} \\ i_{\beta} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -1/2 & -1/2 \\ 0 & \sqrt{3/2} & -\sqrt{3/2} \end{bmatrix} \begin{bmatrix} i_{La} \\ i_{Lb} \\ i_{Ic} \end{bmatrix}$$

(3)

$$\begin{bmatrix} i_d \\ i_q \end{bmatrix} = \begin{bmatrix} \cos \theta & \sin \theta \\ -\sin \theta & \cos \theta \end{bmatrix} \begin{bmatrix} i_\alpha \\ i_\beta \end{bmatrix} \tag{4}$$

$$\begin{bmatrix} i_{\alpha dc} \\ i_{\beta qc} \end{bmatrix} = \begin{bmatrix} \cos \theta & \sin \theta \\ -\sin \theta & \cos \theta \end{bmatrix} \begin{bmatrix} i_{ddc} \\ i_{qdc} \end{bmatrix}$$

(5)

$$\begin{bmatrix} i_{sa}^* \\ i_{sb}^* \\ i_{sc}^* \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \frac{1}{\sqrt{2}} & 1 & 0 \\ \frac{1}{\sqrt{2}} & -\frac{1}{2} & \frac{\sqrt{3}}{2} \\ \frac{1}{\sqrt{2}} & -\frac{1}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} i_0^* \\ i_{\alpha dc}^* \\ i_{\beta dc}^* \end{bmatrix}$$

(6)

The reference load voltages (V\*La, V\*Lb, V\*Lc) in the ABC frame arc were obtained from the reverse park's transformation. The errors between the sensed load voltages (VLa, VLb, VLc) and reference load voltages are used in the PWM controller to generate gate pulses for the VSc. SRF theory is mainly used for extracting reference current. SRF theory measured phase angle and magnitude.

Figure 3. Synchronous reference frame theory

#### 4. RESULTS AND DISCUSSION

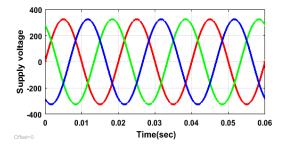

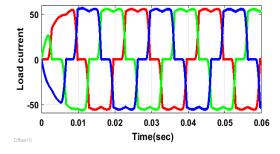

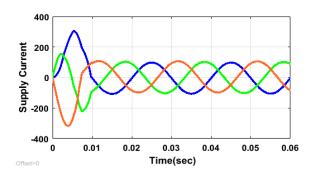

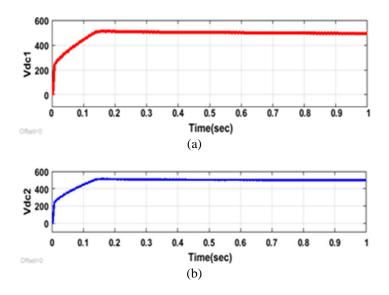

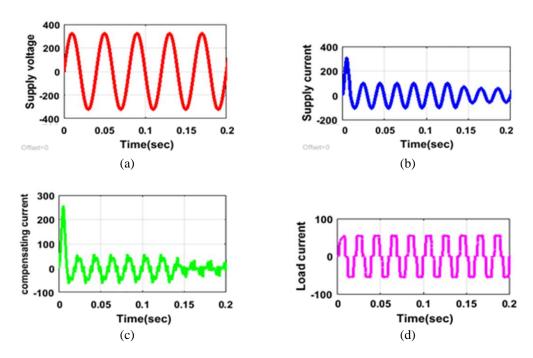

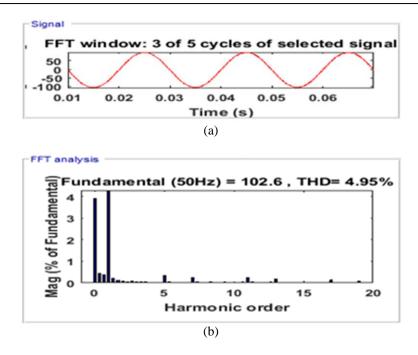

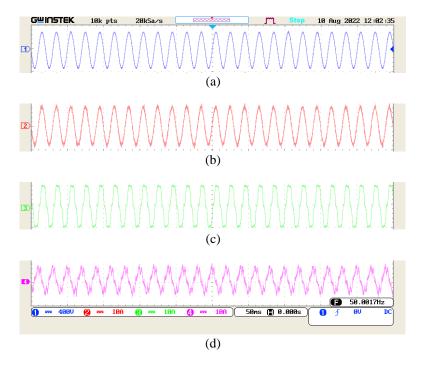

The simulation results of three-phase three-wire DSTATCOM Results are presented in this section. Table 1 shows the simulation results table. Figure 4 shows the source voltage waveform in the distribution system. The source voltage waveform is pure sine wave. Figure 5 shows the load current waveforms, the load current has tripled harmonics. Figure 6 shows the source current waveform, the source current waveform highly distorted 0 to 0.01 sec the magnitude of the current doubles the fundamental current, the DSTATCOM compensated harmonics and maintained sine waveform. The Figure shows the DC link capacitor voltage waveforms of the first leg. Figure 7(a) shows the Leg-A capacitor one voltage and Figure 7(b) shows the Leg-A capacitor two voltage. Figure 8 shows the all-single-phase current waveforms. Figure 8(a) shows the source voltage, Figure 8(b) shows the source current, Figure 8(c) shows the compensating current, and Figure 9(b) source current THD. The THD value is 4.95%. Figure 10 shows the experimental results of DSTATCOM with steady-state conditions. Figure 10(a) shows the source voltage, Figure 10(b) shows the source current, Figure 10(c) shows the load current waveform, and Figure 10(d) shows the compensating current.

| Table 1. Simulation results |                     |             |

|-----------------------------|---------------------|-------------|

| S.L.                        | Criteria            | Achievement |

| 1                           | Source voltage      | 230 V       |

| 2                           | Source Current      | 100 A       |

| 3                           | Load current        | 50 A        |

| 4                           | Dc link voltage     | 500 V       |

| 5                           | Switching frequency | 100 kHz     |

Figure 4. Three-phase source voltage

Figure 5. Three-phase load current

Figure 6. Three-phase source current

Figure 7. DC link capacitor voltages for Leg-A capacitor in (a) one voltage and (b) two voltages

Figure 8. Simulation waveforms of DSTATCOM in (a) single phase source voltage, (b) source current, (c) compensating current, and (d) load current

330 ☐ ISSN: 2252-8814

Figure 9. Source current THD waveform in (a) source current and (b) source current THD

Figure 10. Hardware results of DSTATCOM in (a) single phase source voltage, (b) source current, (c) compensating current, and (d) load current

## 5. CONCLUSION

This paper presents CHBMLI-based DSTATCOM. The proposed topology improved power quality in the distortion system. The proposed topology is controlled by the PI controller. The proposed system simulations are verified in MATLAB/Simulink software. The verified results are source current, load current, and compensating current. The experimental results are verified in OPAL-RT. The steady-state results are verified in real-time. This paper outcome reactive power compensation, source current harmonics elimination, and maintain unity power factor.

#### REFERENCES

- [1] D. Suresh, D. M. Rao, and G. D. Sukumar, "Reduced rating hybrid DSTATCOM for three phase four wire distribution system," in 2016 IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), Jul. 2016, pp. 1–4, doi: 10.1109/ICPEICES.2016.7853646.

- [2] C. Kumar, M. K. Mishra, and S. Mekhilef, "A new voltage control strategy to improve performance of DSTATCOM in electric grid," CES Transactions on Electrical Machines and Systems, vol. 4, no. 4, pp. 295–302, Dec. 2020, doi: 10.30941/CESTEMS.2020.00036.

- [3] B. Singh, P. Jayaprakash, S. Kumar, and D. P. Kothari, "Implementation of neural-network-controlled three-leg VSC and a transformer as three-phase four-wire DSTATCOM," *IEEE Transactions on Industry Applications*, vol. 47, no. 4, pp. 1892–1901, Jul. 2011, doi: 10.1109/TIA.2011.2153811.

- [4] M. A. Eldery, E. F. El-Saadany, and M. M. A. Salama, "DSTATCOM effect on the adjustable speed drive stability boundaries," IEEE Transactions on Power Delivery, vol. 22, no. 2, pp. 1202–1209, Apr. 2007, doi: 10.1109/TPWRD.2007.893617.

- [5] T. S. Saggu, L. Singh, and B. Gill, "Harmonics mitigation in a steel industry using 11-level cascaded multilevel inverter-based DSTATCOM," Canadian Journal of Electrical and Computer Engineering, vol. 40, no. 2, pp. 110–115, 2017, doi: 10.1109/CJECE.2017.2681686.

- [6] W. Freitas, A. Morelato, W. Xu, and F. Sato, "Impacts of AC generators and DSTATCOM devices on the dynamic performance of distribution systems," *IEEE Transactions on Power Delivery*, vol. 20, no. 2, pp. 1493–1501, Apr. 2005, doi: 10.1109/TPWRD.2004.839181.

- [7] B. Singh and J. Solanki, "Load compensation for diesel generator-based isolated generation system employing DSTATCOM," IEEE Transactions on Industry Applications, vol. 47, no. 1, pp. 238–244, Jan. 2011, doi: 10.1109/TIA.2010.2090847.

- [8] B. Singh, M. Kandpal, and I. Hussain, "Control of grid tied smart PV-DSTATCOM system using an adaptive technique," *IEEE Transactions on Smart Grid*, vol. 9, no. 5, pp. 3986–3993, Sep. 2018, doi: 10.1109/TSG.2016.2645600.

- [9] B. Singh and J. Solanki, "A comparison of control algorithms for DSTATCOM," *IEEE Transactions on Industrial Electronics*, vol. 56, no. 7, pp. 2738–2745, Jul. 2009, doi: 10.1109/TIE.2009.2021596.

- [10] R. R. Chilipi, B. Singh, and S. S. Murthy, "Performance of a self-excited induction generator with DSTATCOM-DTC drive-based voltage and frequency controller," *IEEE Transactions on Energy Conversion*, vol. 29, no. 3, pp. 545–557, Sep. 2014, doi: 10.1109/TEC.2014.2321184.

- [11] K. Chenchireddy, V. Kumar, K. R. Sreejyothi, and P. Tejaswi, "A review on D-STATCOM control techniques for power quality improvement in distribution," in 2021 5th International Conference on Electronics, Communication and Aerospace Technology (ICECA), Dec. 2021, pp. 201–208, doi: 10.1109/ICECA52323.2021.9676019.

- [12] V. Kumar, K. Chenchireddy, M. R. Reddy, B. Prasad, B. Preethi, and D. S. Raj, "Power quality enhancement in 3-phase 4-wire distribution system using custom power devices," in 2022 8th International Conference on Advanced Computing and Communication Systems (ICACCS), Mar. 2022, pp. 1225–1228, doi: 10.1109/ICACCS54159.2022.9785339.

- [13] K. Santhosh, K. Chenchireddy, P. Vaishnavi, A. Greeshmanth, V. M. Kumar, and P. N. Reddy, "Time-domain control algorithms of DSTATCOM in a 3-phase, 3-wire distribution system," in 2023 International Conference on Intelligent Data Communication Technologies and Internet of Things (IDCIoT), Jan. 2023, pp. 781–785, doi: 10.1109/IDCIoT56793.2023.10053535.

- [14] V. Kumar, K. Chenchireddy, K. R. Sreejyothi, T. Usha, A. Venkatasaireddy, and B. Rakesh, "Distribution system power quality improvement using IRP theory," in 2023 7th International Conference on Computing Methodologies and Communication (ICCMC), Feb. 2023, pp. 1450–1454, doi: 10.1109/ICCMC56507.2023.10084162.

- [15] T. Madhubabu, A. Anireddy, N. Sahithi, K. S. Krishna Suman, S. Vikas, and K. Chenchireddy, "Reduction of harmonics to improve power quality in distribution lines using a series active power filter," in 2023 7th International Conference on Trends in Electronics and Informatics (ICOEI), Apr. 2023, pp. 123–128, doi: 10.1109/ICOEI56765.2023.10126006.

- [16] K. R. Sreejyothi, S. Umesh, V. R. Kumar, K. Chenchireddy, Y. A. Sai, and B. Nagarjun, "Reduction of THD and power quality improvement by using 48-pulse GTO-based UPFC in the transmission systems," in 2023 7th International Conference on Computing Methodologies and Communication (ICCMC), Feb. 2023, pp. 1466–1470, doi: 10.1109/ICCMC56507.2023.10083821.

- [17] K. Chenchireddy and V. Jegathesan, "Cascaded H-bridge multilevel inverter-based DSTATCOM with an artificial neural fuzzy inference systembased controller," *Indonesian Journal of Electrical Engineering and Computer Science*, vol. 32, no. 1, p. 43, Oct. 2023, doi: 10.11591/ijeecs.v32.i1.pp43-51.

- [18] I. Hussain, R. K. Agarwal, and B. Singh, "Delayed LMS based adaptive control of PV-DSTATCOM system," in 2020 3rd International Conference on Energy, Power and Environment: Towards Clean Energy Technologies, Mar. 2021, pp. 1–6, doi: 10.1109/ICEPE50861.2021.9404442.

- [19] D. Azhagesan, P. Muthuvel, and S. K. Jeyaraj, "Proficiency estimation of four-leg DSTATCOM for compensating load of arc furnace in the distribution system," in 2019 IEEE International Conference on Clean Energy and Energy Efficient Electronics Circuit for Sustainable Development (INCCES), Dec. 2019, pp. 1–5, doi: 10.1109/INCCES47820.2019.9167744.

- [20] A. Elnahdy, "A single-phase current vector control for a DSTATCOM installed in distribution systems," in 2011 IEEE GCC Conference and Exhibition (GCC), Feb. 2011, pp. 481–484, doi: 10.1109/IEEEGCC.2011.5752592.

- [21] S. P. Gawande, S. Khan, and M. R. Ramteke, "Voltage sag mitigation using multilevel inverter based distribution static compensator (DSTATCOM) in low voltage distribution system," in 2012 IEEE 5th India International Conference on Power Electronics (IICPE), Dec. 2012, pp. 1–6, doi: 10.1109/IICPE.2012.6450407.

- [22] M. Mangaraj, A. K. Panda, and T. Penthia, "Neural network control technique based sensorless DSTATCOM for the power conditioning," in 2015 Annual IEEE India Conference (INDICON), Dec. 2015, pp. 1–6, doi: 10.1109/INDICON.2015.7443184.

- [23] P. K. Y. Kundela, M. Mangaraj, and S. K. Sudabattula, "Operation of inductively coupled DSTATCOM for power quality enhancement," in 2022 International Mobile and Embedded Technology Conference (MECON), Mar. 2022, pp. 210–214, doi: 10.1109/MECON53876.2022.9752372.

- [24] D. Suresh, T. J. Kumar, and S. P. Singh, "Three-level active neutral point clamped DSTATCOM with interval type-2 fuzzy logic controller," in 2020 International Conference on Computer Communication and Informatics (ICCCI), Jan. 2020, pp. 1–5, doi: 10.1109/ICCCI48352.2020.9104204.

## **BIOGRAPHIES OF AUTHORS**

Thiruveedula Madhu Babu io is received a B.Tech. from JNTU Hyderabad, Hyderabad, India, in 2010 and an M-tech from NIT Calicut 2012 respectively, and pursuing a Ph.D. in Annamalai University, India. He is working presently as an Assistant Professor and HOD at Teegala Krishna Reddy Engineering College, Hyderabad, India. He has presented technical papers in various national and international journals and conferences. He can be contacted at email: madhumk448@gmail.com.

Kalagotla Chenchireddy is received a B.Tech. and M.tech. from JNTU Hyderabad, Hyderabad, India, in 2011 and 2013 respectively, and pursuing Ph.D. in Karunya Institute of Technology and Sciences, Karunyanagar, Coimbatore, TN, India. He is working presently as an Assistant Professor at, Geethanjali College of Engineering and Technology, Keesara Mandal, Hyderabad, Telangana, INDIA. He has presented technical papers at various national and international conferences. His areas of interest include power electronics, power quality, and multilevel inverters. He is a regular reviewer of ISA Transactions, Cybernetics and Systems SCIE journals, IJPEDS, and IJAPE Scopus journals. He can be contacted at email: chenchireddy.kalagotla@gmail.com.

Kama Sreevarsha is gresently a UG student in Electrical and Electronics Engineering, at Teegala Krishna Reddy Engineering College, Hyderabad, India. She has presented technical papers at various International Conferences. His areas of interest include power electronics, power quality, and multilevel inverters. She developed a single-phase inverter at Teegala Krishna Reddy Engineering College, Hyderabad. She can be contacted by email: sreevarshakama@gmail.com.

**Badudhala Praveen** D S S S is presently a UG student in the Electrical and Electronics Engineering Department, at Teegala Krishna Reddy Engineering College, Hyderabad, India. He has presented technical papers at various national and international conferences. His areas of interest include power electronics, power quality, and multilevel inverters. He can be contacted at email: bpraveen63033@gmail.com.

Mohammad Thanveer D S S S D, is presently a UG Student in the Electrical and Electronics Engineering Department, at Teegala Krishna Reddy Engineering College, Hyderabad, India. He has presented technical papers at various National and International Conferences. His areas of interest include Power Electronics, Power quality; and Multilevel inverters. He can be contacted at email: thaneermohammad143@gmail.com.

Ganji Kashinadh (D) S C he is presently UG Student in Electrical and Electronics Engineering Department, Teegala Krishna Reddy Engineering College, Hyderabad, India. . He has presented technical papers in various National and International Conferences. His area of interest includes Power Electronics, Power quality; Multilevel inverters. He can be contacted at email: kashiganji02@gmail.com.