# Novel cascaded switched-diode five level inverter for renewable energy integration

#### Dhasharatha Ghughuloth, Nampally Rajashekar Varma, Donda Adwaith, Shakeer Hussain, Karthik Gundoji, Harshini Samineni

Department of Electrical and Electronics Engineering, Faculty of Electrical and Electronics Engineering, Teegala Krishna Reddy Engineering College, Hyderabad, India

#### Article Info

#### Article history:

Received Oct 10, 2023 Revised Jan 12, 2024 Accepted Jan 17, 2024

#### Keywords:

Cascaded multi-level inverter Full bridge H-bridge Multilevel Sub multilevel inverter

## ABSTRACT

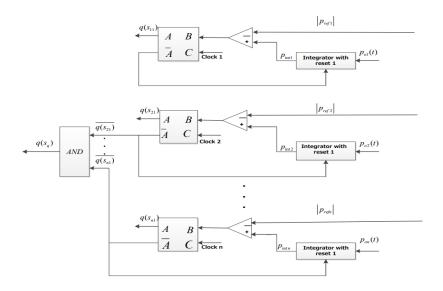

This research presents the usage of a unique five-level cascaded switching diode for medium voltage integration of renewable energy sources. Its primary purpose is to decrease the quantity of gate drivers and switches. In addition to that, the cost and space for the installation of multilevel inverters are less. The inverter topology of novel cascaded multilevel inverters and switched diodes will combine both benefits. One-cycle control (OCC), which is used for clock phase-shifting (CPS) to regulate a two-stage container security device (CSD) multilevel inverter of renewable energy integration, was created to address issues with the multilevel inverter's direct current (DC) source variations. The topology also provides efficiency, harmonic distortion reduction, and voltage output quality. Waveforms are created, and a robust resistance to DC source variations is attained. The viability of the unique five-level inverter using cascaded switched diodes is confirmed by discussing the results of both simulation and experiment.

This is an open access article under the <u>CC BY-SA</u> license.

## **Corresponding Author:**

Dhasharatha Ghughuloth Department of Electrical and Electronics Engineering, Faculty of Electrical and Electronics Engineering Teegala Krishna Reddy Engineering College Medbowli, Meerpet, Saroornagar, Hyderabad-500097, Telangana, India Email: g.dhasharatha@gmail.com

#### 1. INTRODUCTION

A multilevel inverter's primary function is to convert several direct current (DC) voltage levels into the required voltage. A power electrical device known as a multilevel inverter can use many lower-level DC voltages as input and produce a desired alternating voltage level at the output. Power switches operate at a relatively low frequency, but a multilayer inverter may produce high-quality voltage waveforms [1]–[3]. Several multilevel inverter topologies over the previous ten years were showcased. Furthermore, we have been researching the renewable energy integration system extensively. The multilevel inverter-based renewable energy integration system block diagram [4]. To generate the efficient alternating current (AC) from multiple DC through a novel multi-source cascaded multilevel inverter. A five-level inverter can be made up of four diodes one switching element and two capacitors as a voltage divider. It can control the reactive and real power flow also for a five-level inverter does not require any clamping diode. To achieve the number of voltage levels no transformers are required. A balancing capacitor shares a single DC source [5]–[8]. A five-level inverter can produce an output voltage with five clear-cut levels. Maximum positive voltage (Vmax), maximum negative voltage (-Vmax), two intermediate positive voltage levels, and two intermediate negative voltage levels are among the voltage values included in a five-level inverter. These voltage levels allow the inverter to generate a clear AC waveform compared to other voltage inverters with a small number of levels. It is a powerful electronic device used in multiple applications [9]–[12].

The main part of renewable energy integration is to maximize the use of clean and sustainable energy while making sure of the reliability, stability, and efficiency of the electrical grid [13]. Cascaded multilevel converters utilize fewer switching components to achieve the same number of output voltage levels as diode-clamped and flying capacitor multilevel inverters. To improve the overall efficiency of a converter and reduce the switching losses by the soft switching techniques. By using the suitable DC voltage source ratio and modulation method the total harmonic distortion (THD) of the output voltage [14]–[16]. To maintain stable and consistent power quality a five-level inverter can help enhance power quality which is critical for a sensitive load and equipment connected to a grid. For monitoring and control with communication interfaces for many contemporary inverters [17]. In a power system, the cascaded H-bridge inverters are developed for voltage regulation, the utility interface of renewable energy, and VAr compensation harmonic filtering. In a cascaded five-level inverter. The harmonic content decreases as the number of output levels rises and also filter circuit is avoided [18]-[20]. In a renewable energy integration, the inverter may intend to work seamlessly with energy storage systems such as batteries. A novel cascaded five-level inverter can effectively convert renewable DC power into grid-compatible AC power. The twostage cascaded five-level inverter mainly aims to identify the issues related to the DC voltage source, complexity, and switching losses related to the cascaded H-bridge five-level inverter. It is mainly designed and controlled to evaluate the strategy through simulation to imply the advantages for high power applications and middle-high voltage. The second stage of a H-bridge inverter can only operate under power frequency conditions, and it can reduce the switching losses. The control method combines hysteresis losses and carrier cascading modulation [21]-[24]. A cascaded multilevel inverter can produce different output voltage levels. The two-stage cascaded five-level inverter is divided into two stages, here the name itself says that it is two stages. Those two stages are the preceding stage and the backward stage [25].

#### 2. DIODE FIVE-LEVEL INVERTER WITH TWO-STAGE CASCADED SWITCHING

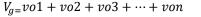

The novel cascaded five-level inverters in the figure aim to reduce gate drivers and the number of switches. Which consists of a bridge inverter, a bidirectional switch, and an auxiliary circuit as well as a metal oxide semiconductor field effect transistor (MOSFET) or an insulated gate bipolar transistor (IGBT). The function of these IGBT is to allow the DC sources to be connected or disconnected from the output. The output voltage is five levels +2vdc, +vdc,0, -vdc, and -2vdc i.e., Vdc refers to each voltage of the DC source as shown in Figure. 1. The CHB five-level topology can be controlled by various pulse width modulation (PWM) techniques such as hybrid PWM, multilevel PWM or SRF14. The five-level topology is a multilevel inverter that can generate five different levels of voltage outputs from two separate DC sources. Auxiliary circuits are used to boost the output of the voltage. CHB five-level topology reduces switching losses, and an improved output waveform can also feed multiple DC loads. The number of switches needed for a N level output voltage, as seen in Figure 1, may be generated by each H-bridge at three different output voltage levels: Vdc, 0 Vdc, and -Vdc.

NIGBT=2Nlevel-2, CHB reduces the number of switches in half as proposed by "Babaei" and "Hossein". To decrease switch count, circuit size, cost, control, and complexity, a container security device (CSD) topology is created. Two H-bridge cells are needed for a cascade H-bridge multilevel inverter of one phase, and these cells must be supplied with DC voltage sources to generate output waveforms. As seen in Figure 1, the output of two H-bridges is coupled so that the total output equals the sum of the output of each H-bridge cell.

Output voltage

$$(V) = V_a + V_b$$

(1)

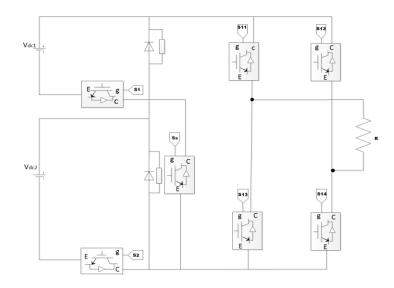

Here, Va=output of first H-bridge; Vb=output of second H-bridge. In modern days, new multilevel inverters are used to reduce switches in topologies, and related gate drivers are developed. The usual cascaded multilevel inverter and the cascaded H-bridge multilevel inverter are the same. The primary drawback of the cascaded h-bridge multilevel inverter, as seen in Figure 2, is that it requires a larger quantity of switches and associated gate drives, which are expensive and need a complicated circuit. Babei and Hosseini proposed a cascaded half-bridge topology that effectively reduces the number of switches this paper presents the topology of a novel cascaded two-stage CSD five level by using a small number of switches for achieving greater voltage levels. Additionally, under R and L loads, a channel for reverse load currents eliminates voltage spikes. A DC voltage source manufactured by IGBT and its internal diode, which are coupled in parallel to prevent the bridge's shoot-through effect, are shown in Figure 2. For V01 of the main unit 1 we obtained two values that are V01 when switch S11 is turned off and when switch P11 is 0 and

335

(2)

conducts and in between unit 2 and unit 5 the pike removal switch sg is connected. When every switch in the unit is off, the switch SG offers a conduit for the reverse load current to pass. Switch SG will then activate. The first level is represented by the cascade arrangement of all basic units and the spike reduction switch sg in Figure 1. The following is the first stage's maximum output as (2).

Figure 1. Structure of proposed two-stage cascaded CSD

Figure 2. CHB multilevel topology

The waveforms of output voltage produced by the first-stage converters resemble positive staircases. It takes a second-stage converter to provide an output voltage that is both positive and negative. Waveforms of voltage and a positive or negative voltage reference are related to the analysis of switch states. Using a second-stage converter will yield the output voltages' positive and negative halves. In the symmetric scenario, the voltages of all the DC voltage sources equal Vdc. The total number of switches and the N level are the output voltage levels. This may be estimated since NIGBT is required.

Novel cascaded switched-diode five level inverter for renewable energy ... (Dhasharatha Ghughuloth)

$$N \, IGBT = n + 5 \tag{3}$$

$$N \ Level = 2n+1 \tag{4}$$

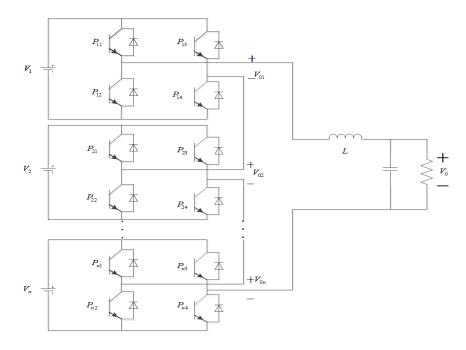

The clock phase-shifting (CPS) One-cycle control (OCC) technique diagram for two-stage CSD shows how the output voltage is precisely controlled by adjusting the clock signal's phase. In two stages CSD inverter consists of two stages. The cascaded switching device inverter consists of two stages. A cascaded switching device for a five-level inverter stage. It usually creates a digital view of the desired output voltage. Which is then converted by the inverter stage to an analog voltage. The second stage is the inverter in this analog voltage produced by a cascaded switching device to generate its final output voltage. By manipulating the phase of clock signals, we can control the timing of switches in both the cascaded switching device and the inverter for precise voltage control as shown in Figure 3. According to the table, the second stage implements the positive and negative half cycles of the output waveforms by comparing the reference voltage with zero. The CPS OCC is then constructed for the first stage, and it only corresponds with the positive stage, as seen in Figure 3.

Figure 3. Control diagram of CPS OCC for the two-stage CSD inverter

#### 3. SIMULATION AND RESULTS

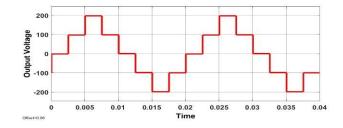

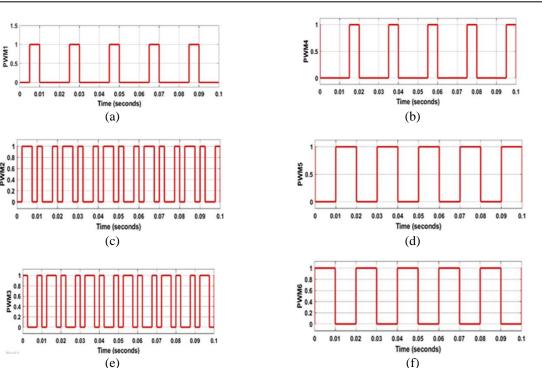

Figure 4 displays the output voltage with five levels. As we know, there are five distinct voltage levels in the square waveform where the output voltage is located in this instance. Here the input DC voltage is 200V in magnitude. In Figure 4, the waveform starts from -100 V and increases up to a maximum of 200 V and starts decreasing from 200 V to -200 V in 5 steps so it is called a five-level inverter. In Figure 4 time is indicated on the X-axis, and the output voltage is represented on the Y-axis. Within Figure 5 The time in seconds is shown by the X-axis, and the PWM input to each thyristor is indicated by Figures 5(a)-(f) the Y-axis. The output waveforms of the active switches after the applications of the PWM technique and we can observe that the magnitude and width of every waveform are different.

Figure 4. The five-level output waveform of the proposed two-stage CSD

337

Figure 5. Output waveforms of active switches after the application of the PWM technique in (a) PWM1, (b) PWM2, (c) PWM3, (d) PWM4, (e) PWM5, and (f) PWM6

#### 4. CONCLUSION

A novel cascaded switched diode five-level inverter produces higher voltage levels and also improves the waveform quality compared to the other two-level inverters. This higher voltage allows the more efficient and reliable energy conversion, reducing power losses and increasing overall system performance. Also, the ability to switch between different voltage levels with a minimum number of switching losses to ensure smooth operation and better performance, mainly in different environmental conditions. Two-stage cascaded switched diode five-level inverter mainly aims to generate an efficient output voltage and it is very suitable for medium voltage renewable energy applications. The full bridge inverter is added as the second stage converter for both positive and negative output voltage levels, and this results in the removal of high voltage spikes caused by the collapsing magnetic field in short time intervals. Additionally, the spike removal switch added in the first stage provides the path for the reverse load current R-L loads. These benefits include reduced component count, lower cost, and improved performance by sending voltage spikes.

#### REFERENCES

- R. Shalchi Alishah, D. Nazarpour, S. H. Hosseini, and M. Sabahi, "Novel topologies for symmetric, asymmetric, and cascade switched-diode multilevel converter with minimum number of power electronic components," *IEEE Transactions on Industrial Electronics*, vol. 61, no. 10, pp. 5300–5310, Oct. 2014, doi: 10.1109/TIE.2013.2297300.

- [2] G. Dhasharatha, B. Mangu, and M. Haseeb Khan, "A novel switched-capacitor based multilevel voltage boost inverter for EV interface," *International Journal of Electronics*, pp. 1–17, Feb. 2024, doi: 10.1080/00207217.2024.2312556.

- [3] S. Vijayalakshmi, M. Marimuthu, B. Sanjeev, S. Sivahari, D. Praveenkumar, and E. C. Sriraman, "Asymmetric cascaded switched diode multilevel inverter," in 2023 4th International Conference for Emerging Technology (INCET), May 2023, pp. 1–5, doi: 10.1109/INCET57972.2023.10170019.

- [4] C. K. Kishore, K. Balaji, and J. Madhavan, "Modified cascaded switched diode multilevel inverter with multiple outputs and reduced harmonic content," in 2019 1st International Conference on Innovations in Information and Communication Technology (ICIICT), Apr. 2019, pp. 1–4, doi: 10.1109/ICIICT1.2019.8741436.

- [5] V. Boorgula and S. S. T. Ram, "Incipient fault diagnosis in stator winding of synchronous generator: a CMFFLC technique," *IETE Journal of Research*, vol. 65, no. 5, pp. 667–678, Sep. 2019, doi: 10.1080/03772063.2018.1447403.

- [6] S. A. A. Ibrahim, A. Palanimuthu, and M. A. J. Sathik, "Symmetric switched diode multilevel inverter structure with minimised switch count," *The Journal of Engineering*, vol. 2017, no. 8, pp. 469–478, Aug. 2017, doi: 10.1049/joe.2017.0174.

- [7] M. A. Hosseinzadeh, M. Sarbanzadeh, E. Sarbanzadeh, M. Rivera, E. Babaei, and J. Riveros, "New cascaded multilevel converters based on switched-diode six-level configuration," in 2017 IEEE Southern Power Electronics Conference (SPEC), Dec. 2017, pp. 1–6, doi: 10.1109/SPEC.2017.8333664.

- [8] G. Singh and V. K. Garg, "THD analysis of cascaded H-bridge multi-level inverter," in 2017 4th International Conference on Signal Processing, Computing and Control (ISPCC), Sep. 2017, pp. 229–234, doi: 10.1109/ISPCC.2017.8269680.

Novel cascaded switched-diode five level inverter for renewable energy ... (Dhasharatha Ghughuloth)

- [9] K. R. Sreejyothi, K. Chenchireddy, N. Lavanya, R. M. Reddy, K. Y. G. Prasad, and R. Revanth, "Level-shifted PWM techniques applied to flying capacitor multilevel inverter," in 2022 International Conference on Electronics and Renewable Systems (ICEARS), Mar. 2022, pp. 41–46, doi: 10.1109/ICEARS53579.2022.9752074.

- [10] N. R. Varma, D. G, K. Tanuja, G. Avinash, K. S. Reddy, and T. S. Teja, "15 Level inverter for stand-alone applications," in 2023 7th International Conference on Computing Methodologies and Communication (ICCMC), Feb. 2023, pp. 1439–1443, doi: 10.1109/ICCMC56507.2023.10083851.

- [11] D. G, N. R. Varma, A. Spandana, P. A. Kumar, B. Venumadhav, and B. P. Kumar, "Design and implementation of three-phase three level NPC inverter," in 2023 7th International Conference on Trends in Electronics and Informatics (ICOEI), Apr. 2023, pp. 106–110, doi: 10.1109/ICOEI56765.2023.10125979.

- [12] N. R. Varma, D. G, E. H. V. Reddy, A. Manisha, M. T. Kumar, and K. Charan, "Output voltage and power factor improvement for non-conventional energy generation," in 2023 7th International Conference on Trends in Electronics and Informatics (ICOEI), Apr. 2023, pp. 151–156, doi: 10.1109/ICOEI56765.2023.10125899.

- [13] D. G, R. Varma, B. V. Ramana, K. Madhu, J. C. Shekar, and G. Nithin, "Z-source inverter for standalone application," in 2023 8th International Conference on Communication and Electronics Systems (ICCES), Jun. 2023, pp. 26–31, doi: 10.1109/ICCES57224.2023.10192666.

- [14] D. Baimel and S. Tapuchi, "A new topology of cascaded multilevel inverter," in *Proceedings ELMAR-2013*, 2013, pp. 137–140.

- [15] R. A. Thakur and T. Dixit, "Novel 5 level cascaded H-bridge multilevel inverter topology," International Journal of Engineering Trends and Technology (IJETT), vol. 24, no. 2, 2015.

- [16] S. Khomfoi and C. Aimsaard, "A 5-level cascaded hybrid multilevel inverter for interfacing with renewable energy resources," in 2009 6th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology, May 2009, pp. 284–287, doi: 10.1109/ECTICON.2009.5137009.

- [17] A. Gaikwad and P. A. Arbune, "Study of cascaded H-bridge multilevel inverter," in 2016 International Conference on Automatic Control and Dynamic Optimization Techniques (ICACDOT), Sep. 2016, pp. 179–182, doi: 10.1109/ICACDOT.2016.7877574.

- [18] V. Aishwarya and K. G. Sheela, "Topologies and comparative analysis of reduced switch multilevel inverters for renewable energy applications," in *Power Electronics for Green Energy Conversion*, Wiley, 2022, pp. 221–264.

- [19] R. Jawahar and M. Santhi, "A novel design of multilevel inverter with reduced switch topology for the integration of renewable energy sources," *Journal of Electrical Engineering*, vol. 19, no. 3, 2019.

- [20] A. Akbari and A. Bakhshai, "A novel multilevel inverter structure for renewable energy applications," in 2023 IEEE 14th International Conference on Power Electronics and Drive Systems (PEDS), Aug. 2023, pp. 1–6, doi: 10.1109/PEDS57185.2023.10246539.

- [21] S.-A. Amamra, K. Meghriche, A. Cherifi, and B. Francois, "Multilevel inverter topology for renewable energy grid integration," *IEEE Transactions on Industrial Electronics*, vol. 64, no. 11, pp. 8855–8866, Nov. 2017, doi: 10.1109/TIE.2016.2645887.

- [22] A. K. Yarlagadda and V. Verma, "A novel multilevel inverter topology with reduced number of component count and total standing voltage for renewable energy conversion system," *Renewable Energy Focus*, vol. 43, pp. 84–92, Dec. 2022, doi: 10.1016/j.ref.2022.09.004.

- [23] S. S. Lee, Y. Yang, Y. P. Siwakoti, and K.-B. Lee, "A novel boost cascaded multilevel inverter," *IEEE Transactions on Industrial Electronics*, vol. 68, no. 9, pp. 8072–8080, Sep. 2021, doi: 10.1109/TIE.2020.3016252.

- [24] K. P. Panda, S. S. Lee, and G. Panda, "Reduced switch cascaded multilevel inverter with new selective harmonic elimination control for standalone renewable energy system," *IEEE Transactions on Industry Applications*, vol. 55, no. 6, pp. 7561–7574, Nov. 2019, doi: 10.1109/TIA.2019.2904923.

- [25] A. Chen, L. Hu, and X. He, "A novel cascaded multilevel inverter topology," in 30th Annual Conference of IEEE Industrial Electronics Society, 2004. IECON 2004, vol. 1, pp. 796–799, doi: 10.1109/IECON.2004.1433416.

#### **BIOGRAPHIES OF AUTHORS**

**Dhasharatha Ghughuloth b X s** received the B.Tech. degree in electrical and electronics engineering from Jawaharlal Nehru Technological University Hyderabad in 2010, and the M.Tech. degree in power systems from the National Institute Technological Calicut, Kerela in 2013. He has 09 years of experience in Teaching and presently working as an Assistant Professor in the Department of Electrical and Electronics Engineering, TKREC. His research interests are multilevel inverters, renewable energy sources, power quality improvement, and FACTS controllers. He can be contacted at email g.dhasharatha@gmail.com.

**Nampally Rajashekar Varma b S s c** received a Ph.D. from JNTU Anantapur Andhra Pradesh in 2019. He is working presently as a professor at Teegala Krishna Reddy Engineering College Hyderabad India. He has presented technical papers in various national and international journals and conferences.his areas of interest include power quality, smart grids, and electric vehicles. He can be contacted at email: drnrsvarma@gmail.com.

**D** 339

**Donda Adwaith D S S C** is presently a UG student in the Department of Electrical and Electronics Engineering, at Teegala Krishna Reddy Engineering College, Hyderabad, India. He has presented technical papers in various national and international journals and conferences. His area of interest includes power system inverters and power electronics. He developed a hybrid vehicle in Teegala Krishna Reddy Engineering College Hyderabad. He can be contacted at email: adwaith.donda@gmail.com.

**Shakeer Hussain** State is presently a UG student in the Electrical and Electronics Engineering Department, at Teegala Krishna Reddy Engineering College, Hyderabad, India. He has presented technical papers in various national and international journals and conferences. His area of interest includes power system inverters and power electronics. He developed a hybrid vehicle in Teegala Krishna Reddy Engineering College Hyderabad. He can be contacted at email: gmshakeer786@gmail.com.

**Karthik Gundoji S S i**s presently a UG student in the Electrical and Electronics Engineering Department, at Teegala Krishna Reddy Engineering College, Hyderabad, India. He has presented technical papers in various national and international journals and conferences. His area of interest includes power system inverters and power electronics. He developed a hybrid vehicle in Teegala Krishna Reddy Engineering College Hyderabad. He can be contacted at email: gundoijukarthikkarthik@gmail.com.

**Harshini Samineni b s s c** is presently a UG student in the Department of Electrical and Electronics Engineering, at Teegala Krishna Reddy Engineering College, Hyderabad, India. She has presented technical papers in various national and international journals and conferences. Her area of interest includes power system inverters and power electronics. She developed a hybrid vehicle in Teegala Krishna Reddy Engineering College Hyderabad. She can be contacted at email: samineniharshini@gmail.com.